Téma: Cmos reset

Mam otazku ohladom resetu cmosu, konkretne CD4060 v datasheete pisu ze by na reset pine nemalo byt vyssie napatie ako Vdd+0,5V...

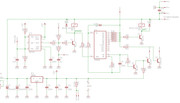

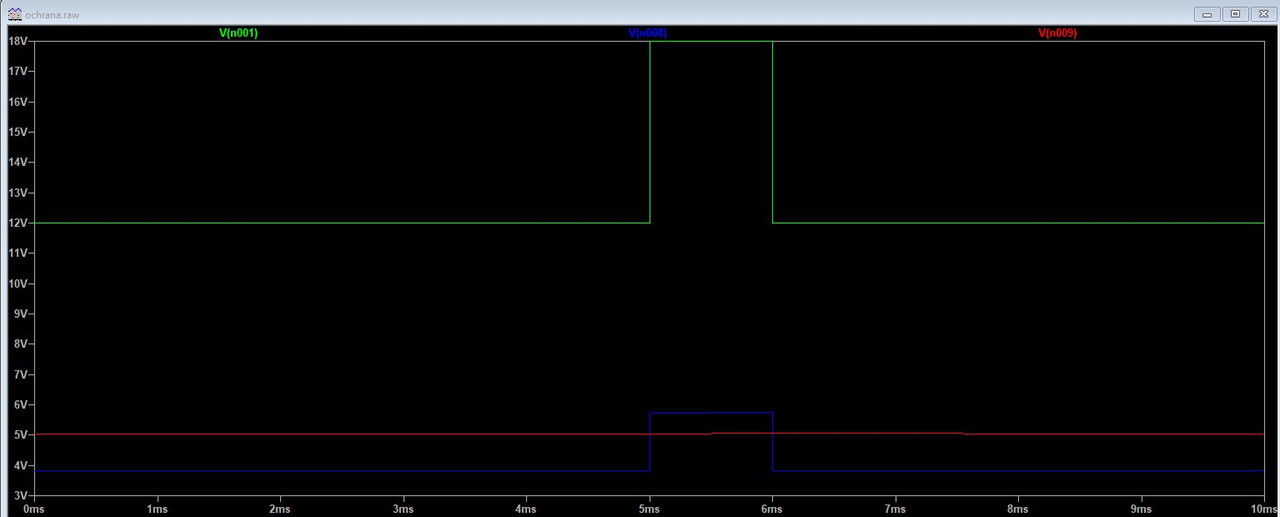

cmos mam napajany nizsim napatim (+5V) ako mam napatie ktore pouzivam na napajanie resetu (odpojena civka rele +12V), ak prepojim tychto 12V do reset pinu cez 100k odpor tak sa napatie na tomto reset pine automaticky asi nejakym prechodom (alebo vnutornou ochranou?) ustali na 5,5V

Je toto problem ktory treba nejako riesit? napr. dat na tento vstup 5V1 zenerku, alebo je to takto vporiadku a cmos bude fungovat bez poruchy dlhodobo?

dik za tipy

dik za tipy

Nahrát obrázek

Nahrát obrázek