Jestli myslíš ESCC, tak tohle tam není nijak omezený, pouze ti to musí projít vibračníma a termálníma testama (100x -40 až 150°C, pak 20 minut vibračky, kde špičkový přetížení je až 1000G a pak zase 100 teplotních cyklů...následně se spoj rozřeže, vyleští a kontroluje na praskliny), nicméně se pro space ani nic pod 6 vrstevj nepoužívá  U jednostranky to teda fakt netuším.

U jednostranky to teda fakt netuším.

Na druhou stranu ty podmínky pájení a kvalita výroby desek jsou tak přísný, že se to nejspíš nestane ani s tím padem z Eaglu. Taky ta výroba desek stojí pěkné penízky, za 120x120mm panel cca 1000€ (jestli si myslíte, že to je hodně, tak FPGA s papírama stojí asi 9000€, "obyčený" 4 násobný NAND hradlo 300€ a často jsou minimálně odběry 10ks+, viz třeba toto: http://cz.mouser.com/ProductDetail/Texa … RUGxRUDvYW ).

U jednostranky jsem zvyklej používat alespoň 1,5× d vývodu součástky jako vzdálenost mezi dírou a okrajem padu, ostatně podobně to používám i když kreslím něco v práci.

https://escies.org/download/webDocumentFile?id=48636 tady je ESCC norma na manuální pájení THT, možná to tam bude...

U jednostranky to teda fakt netuším.

U jednostranky to teda fakt netuším.

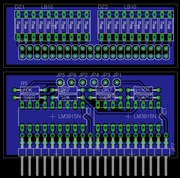

Nahrát obrázek

Nahrát obrázek